ViewSonic G90FB-4 - Model No. VS10794 - 19” Digital Controlled Color Monitor - Schematic Diagrams _ Power, Horizontal Out & System control

Click on the schematics to Zoom In

SMPS

Before check SW.REG

Variable output: 60V

Constant output: 6.3V, 12V, 83V,180.V, -12V

Adjustment conditions and precautions

Adjustments should be undertaken only on those necessary elements since most of them have been carefully preset at the factory.

The B+ control block of the SAA4849 has the same behavior as the TDA4856 with adapted threshold voltages. The circuit allows the user to choose the trigger edge of the HDRV signal and the polarity of the output stage via I2C-Bus. The B+ control function block of the SAA4849 consists of an Operational Trans conductance Amplifier (OTA), a voltage comparator, a flip-flop and a discharge circuit. This configuration allows easy application for different B+ control concepts.

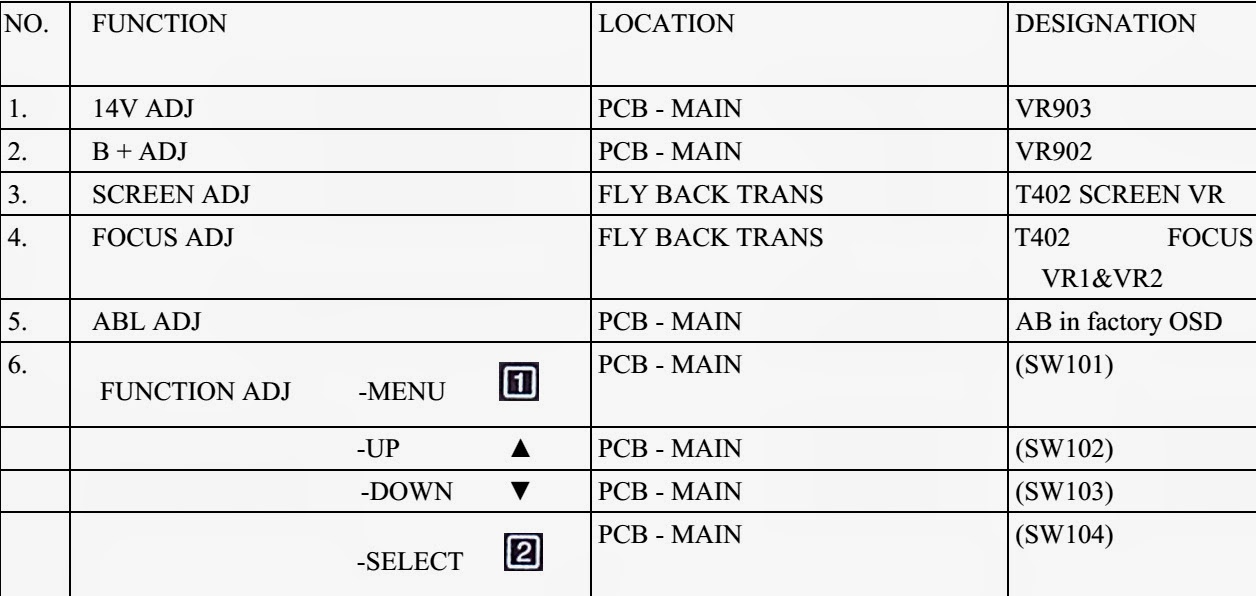

Main adjustments:

Power supply Troubleshoot

The horizontal part contains a PLL, which works over the full frequency range from 25 kHz to 140 kHz. This range can be reduced by a over and an upper frequency limit (Write Once Registers HPMAX and HPMIN).Via I2C bus the number of 48MHz clock cycles is sent through the register. The slewing speed during mode change is also programmable in a write once register (HSLEW) After the clocks for the HPLL are switched on, the HPLL starts with a fixed free running frequency of 60 kHz. The H-drive pulses are not active and the start up procedure is inhibited. The default setting of register bit HCONTROL [0] will cause the HPLL to slew, not switch. To the free running frequency defined in the I2C register HPFREE (the default value is also 60 kHz).Independent on H-syncs which are possibly present. The HPLL will slew to that free running frequency. To achieve an always defined starting point for the startup procedure, this procedure cannot be interrupted.

Horizontal scan & output schematic

Micro-controller Section

The micro controller (IC101) core is a 80C51 type. The micro clock frequency of 12 MHz is derived from the Xtal oscillator, which is running at 48MHz. The DDC interface is suitable to handle DDC2 by a modified hardware I2C-bus interface .Standard high current ports,3 ADC pouts with voltage inputs and 4 static standard8 bit DAC outputs (low interference) and one PWM output for digital control application are implemented. The central processing unit (CPU) manipulates operands in two memory spaces. These are the 1024byte internal data memory (consisting of 256 bytes standard RAM and 768 bytes AUX-RAM) and 48K-byte internal program memory. The program memory of the SAA4849 consists of 48K bytes ROM. The SAA4849P provides sync. Processing with full auto sync. Capability, a flexible SMPS block and an extensive set of geometry control facilities. Further the IC generates the drive waveforms for DC coupled vertical boosters to the TDA8172.