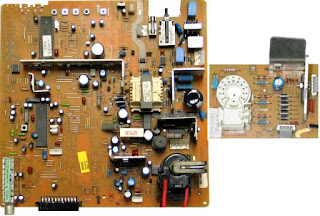

PAL B/G / SECAM L/L’, B/G, D/K SYSTEM COLOUR TELEVISION: AK-44 Chassis

11AK44 is a 90° chassis capable of driving 20"/21" tubes at the appropriate currents. The chassis is capable of operating in PAL, SECAM and NTSC standards. The sound system is capable of giving 4 watts RMS output into a load of 16 ohms.

The chassis in this receiver is partially hot. Use an isolation transformer between the line cord plug and power receptacle, when servicing this chassis.

White Level

Apply the rated voltage at the rated frequency to the TV set, while it is receiving full white pattern RF signal of 60 dB/µV from its RF input via the pattern generator.

Turn all picture controls to maximum value. Measure the colour temperatures at the center of the screen by using the colour analyzer.

X=0.290 ± 0.015 Y=0.300 ± 0.015

Apply the rated voltage at the rated frequency to the TV set, while it is receiving full white pattern RF signal of 60 dB/µV from its RF input via the pattern generator.

Turn all picture controls to maximum value. Measure the colour temperatures at the center of the screen by using the colour analyzer.

X=0.290 ± 0.015 Y=0.300 ± 0.015

It is important that the static charge is removed from the high voltage system when carrying out work on the receiver. This can be achieved by connecting a 10K resistor (with a suitably insulated lead) from the CRT cavity connector to the CRT ground tag. This must be carried out with the AC supply disconnected from the receiver.

DO NOT increase the EHT to more than 29.5 KV, (at a instantaneous beam current of 1150 µA

This level has been preset in the factory. Always check that this level has not been exceeded after carrying out any repair on the receiver.

To update the Technical Information

Web site: https://www.vestelservice.com

Select: Technical Support

Login: 101278

Password: SHPII278

Select: Technical Support

Login: 101278

Password: SHPII278

By this access you can consult the latest schematic diagram or request the Parts Listing of a concrete Production Date / Serial Number.

PERI-TV SOCKET connections detailVision IF amplifier

The vision IF amplifier can demodulate signals with positive and negative modulation. The PLL demodulator is completely alignment-free. Although the VCO (Toko-coil) of the PLL circuit is external, yet the frequency is fixed to the required value by the original manufacturer thus the Toko-coil does not need to be adjusted manually. The setting of the various frequencies (38.9 or 33,8 MHz) can be made via changing the coil itself.

The vision IF amplifier can demodulate signals with positive and negative modulation. The PLL demodulator is completely alignment-free. Although the VCO (Toko-coil) of the PLL circuit is external, yet the frequency is fixed to the required value by the original manufacturer thus the Toko-coil does not need to be adjusted manually. The setting of the various frequencies (38.9 or 33,8 MHz) can be made via changing the coil itself.

QSS Sound circuit (QSS versions)

The sound IF amplifier is similar to the vision IF amplifier and has an external AGC de-coupling capacitor. The single reference QSS mixer is realised by a multiplier. In this multiplier the SIF signal is converted to the inter-carrier frequency by mixing it with the regenerated picture carrier from the VCO. The mixer output signal is supplied to the output via a high-pass filter for attenuation of the residual video signals. With this system a high performance hi-fi stereo sound processing can be achieved. The AM sound demodulator is realized by a multiplier. The modulated sound IF signal is multiplied in phase with the limited SIF signal. The demodulator output signal is supplied to the output via a low-pass filter for attenuation of the carrier harmonics. The AM signal is supplied to the output via the volume control.

The sound IF amplifier is similar to the vision IF amplifier and has an external AGC de-coupling capacitor. The single reference QSS mixer is realised by a multiplier. In this multiplier the SIF signal is converted to the inter-carrier frequency by mixing it with the regenerated picture carrier from the VCO. The mixer output signal is supplied to the output via a high-pass filter for attenuation of the residual video signals. With this system a high performance hi-fi stereo sound processing can be achieved. The AM sound demodulator is realized by a multiplier. The modulated sound IF signal is multiplied in phase with the limited SIF signal. The demodulator output signal is supplied to the output via a low-pass filter for attenuation of the carrier harmonics. The AM signal is supplied to the output via the volume control.

FM demodulator and audio amplifier (mono versions)

The FM demodulator is realized as narrow-band PLL with external loop filter, which provides the necessary selectivity without using an external band-pass filter. To obtain a good selectivity a linear phase detector and constant input signal amplitude are required. For this reason the inter-carrier signal is internally supplied to the demodulator via a gain controlled amplifier and AGC circuit. The nominal frequency of the demodulator is tuned to the required frequency (4.5/ 5.5/6.0/6.5 MHz) by means of a calibration circuit that uses the clock frequency of the µ-controller/Teletext decoder as a reference. The setting to the wanted frequency is realized by means of the software. It can be read whether the PLL frequency is inside or outside the window and whether the PLL is in lock or not.

With this information it is possible to make an automatic search system for the incoming sound frequency. This is realized by means of a software loop that alternate the demodulator to various frequencies, then select the frequency on which a lock condition has been found. De-emphasis output signal amplitude is independent of the TV standard and has the same value for a frequency deviation of ±25 kHz at the 4.5 MHz standard and for a deviation of ±50 kHz for the other standards. When theIF circuit is switched to positive modulation the internal signal on de-emphasis pin is automatically muted. The audio control circuit contains an audio switch and volume control. In the mono inter-carrier sound versions the Automatic Volume Levelling (AVL) function can be activated. The pin to which the external capacitor has to be connected depends on the IC version. For the 90° types the capacitor is connected to the EW output pin (pin 20). When the AVL is active it automatically stabilises the audio output signal to a certain level.

The FM demodulator is realized as narrow-band PLL with external loop filter, which provides the necessary selectivity without using an external band-pass filter. To obtain a good selectivity a linear phase detector and constant input signal amplitude are required. For this reason the inter-carrier signal is internally supplied to the demodulator via a gain controlled amplifier and AGC circuit. The nominal frequency of the demodulator is tuned to the required frequency (4.5/ 5.5/6.0/6.5 MHz) by means of a calibration circuit that uses the clock frequency of the µ-controller/Teletext decoder as a reference. The setting to the wanted frequency is realized by means of the software. It can be read whether the PLL frequency is inside or outside the window and whether the PLL is in lock or not.

With this information it is possible to make an automatic search system for the incoming sound frequency. This is realized by means of a software loop that alternate the demodulator to various frequencies, then select the frequency on which a lock condition has been found. De-emphasis output signal amplitude is independent of the TV standard and has the same value for a frequency deviation of ±25 kHz at the 4.5 MHz standard and for a deviation of ±50 kHz for the other standards. When theIF circuit is switched to positive modulation the internal signal on de-emphasis pin is automatically muted. The audio control circuit contains an audio switch and volume control. In the mono inter-carrier sound versions the Automatic Volume Levelling (AVL) function can be activated. The pin to which the external capacitor has to be connected depends on the IC version. For the 90° types the capacitor is connected to the EW output pin (pin 20). When the AVL is active it automatically stabilises the audio output signal to a certain level.

Synchronisation circuit

The video processor (STV224X) performs the horizontal and vertical processing. The external horizontal deflection circuit is controlled via the Horizontal output pulse (HOUT). The vertical scanning is performed through an external ramp generator and a vertical power amplifier IC controlled by the Vertical output pulse (VOUT).

The main components of the deflection circuit are:

• PLL1: the first phase locked loop that locks the internal line frequency reference on the CVBS input signal. It is composed of an integrated VCO (12 MHz) that requires the chroma Reference frequency (4.43 MHz or 3.58 MHz crystal oscillator reference signal), a divider by 768, a line decoder, and a phase comparator.

• PLL2: The second phase locked loop that controls the phase of the horizontal output (Compensation of horizontal deflection transistor storage time variation). Also the horizontal position adjustment is also performed in PLL2.

• A vertical pulse extractor.

• A vertical countdown system to generate all vertical windows (vertical synchronization window, frame blanking pulses, 50/60 Hz identification window...).

• Automatic identification of 50/60 Hz scanning.

• PLL1 time constant control.

• Noise detector, video identification circuits, and horizontal coincidence detector.

• Vertical output stage including de-interlace function, vertical position control.

• Vertical amplitude control voltage output (combined with chroma reference output and Xtal 1 indication).

The video processor (STV224X) performs the horizontal and vertical processing. The external horizontal deflection circuit is controlled via the Horizontal output pulse (HOUT). The vertical scanning is performed through an external ramp generator and a vertical power amplifier IC controlled by the Vertical output pulse (VOUT).

The main components of the deflection circuit are:

• PLL1: the first phase locked loop that locks the internal line frequency reference on the CVBS input signal. It is composed of an integrated VCO (12 MHz) that requires the chroma Reference frequency (4.43 MHz or 3.58 MHz crystal oscillator reference signal), a divider by 768, a line decoder, and a phase comparator.

• PLL2: The second phase locked loop that controls the phase of the horizontal output (Compensation of horizontal deflection transistor storage time variation). Also the horizontal position adjustment is also performed in PLL2.

• A vertical pulse extractor.

• A vertical countdown system to generate all vertical windows (vertical synchronization window, frame blanking pulses, 50/60 Hz identification window...).

• Automatic identification of 50/60 Hz scanning.

• PLL1 time constant control.

• Noise detector, video identification circuits, and horizontal coincidence detector.

• Vertical output stage including de-interlace function, vertical position control.

• Vertical amplitude control voltage output (combined with chroma reference output and Xtal 1 indication).

Chroma and luminance processing

The chroma decoder is able to demodulate PAL, NTSC and SECAM signals.

The decoder dedicated to PAL and NTSC sub-carrier is based on a synchronous demodulator, and an Xtal PLL locked on the phase reference signal (burst).

The SECAM demodulation is based on a PLL with automatic calibration loop.

The color standard identification is based on the burst recognition.

Automatic and forced modes can be selected through the I2C bus.

NTSC tint, and auto flesh are controlled through I2C bus.

Xtal PLL can handle up to 3 crystals to work in PAL M, PAL N and NTSC M for South America.

ACC an ACC overload control the chroma sub-carrier amplitude within 26dB range. Both ACCs are based on digital systems and do not need external capacitor.

All chroma filters are fully integrated and tuned via a PLL locked on Xtal VCO signal.

A second PLL is used for accurate fine-tuning of the SECAM bell filter. This tuning is achieved during the frame blanking.

An external capacitor memorizes the bell filter tuning voltage.

A base-band chroma delay-line rebuilds the missing color line in SECAM and removes transmission phase errors in PAL.

The base-band chroma delay line is clocked with 6 MHz signal provided by the horizontal scanning VCO.

The luminance processor is composed of a chroma trap filter, a luminance delay line, a peaking function with noise coring feature, a black stretch circuit.

Trap filter and luminance delay lines are achieved with the use of bi-quad integrated filters, auto aligned via a master filter phase locked loop.

The chroma decoder is able to demodulate PAL, NTSC and SECAM signals.

The decoder dedicated to PAL and NTSC sub-carrier is based on a synchronous demodulator, and an Xtal PLL locked on the phase reference signal (burst).

The SECAM demodulation is based on a PLL with automatic calibration loop.

The color standard identification is based on the burst recognition.

Automatic and forced modes can be selected through the I2C bus.

NTSC tint, and auto flesh are controlled through I2C bus.

Xtal PLL can handle up to 3 crystals to work in PAL M, PAL N and NTSC M for South America.

ACC an ACC overload control the chroma sub-carrier amplitude within 26dB range. Both ACCs are based on digital systems and do not need external capacitor.

All chroma filters are fully integrated and tuned via a PLL locked on Xtal VCO signal.

A second PLL is used for accurate fine-tuning of the SECAM bell filter. This tuning is achieved during the frame blanking.

An external capacitor memorizes the bell filter tuning voltage.

A base-band chroma delay-line rebuilds the missing color line in SECAM and removes transmission phase errors in PAL.

The base-band chroma delay line is clocked with 6 MHz signal provided by the horizontal scanning VCO.

The luminance processor is composed of a chroma trap filter, a luminance delay line, a peaking function with noise coring feature, a black stretch circuit.

Trap filter and luminance delay lines are achieved with the use of bi-quad integrated filters, auto aligned via a master filter phase locked loop.

µ-Controller

The ST92195 is the micro-controller, which is required for a color TV receiver. ST92195D1 is the version with one page Teletext and ST92195D7 is the one with 7 page Teletext. The IC has the supply voltage of 5 V and they are mounted in PSDIP package with 56 pins.

µ-Controller has the following features

- Display of the program number, channel number, TV Standard, analogue values, sleep timer, parental control and mute is done by OSD

- Single LED for stand-by and on mode indication

- System configuration with service mode

- 3 level logic output for SECAM and Tuner band switching

IC 501 controls all the functions of the receiver operated by the remote control and the front panel customer controls. It produces the on screen graphics, operates tuning, customers controls and engineering controls, and also incorporates all of the Teletext functions. It also controls the video processor, the audio processor, and the tuner. The circuits just mentioned are controlled via the I²C bus. Also IC501 controls the video source switching, vertical position adjustment and the vertical linearity adjustment via its ports.

An external 8K EEPROM is used by the micro. The EEPROM comes fully programmed. The main clock oscillator is 4.0 MHz crystal X501 on pins 50 and 51. Reset is provided on pin 2 via Q504. On switching on pin 2 becomes high and the controller gets reset which stays valid till a low signal comes on that pin.

Controls

Command information from the infrared remote controller is fed through the sensor IC502 to pin 1 of the microprocessor. Operation of the customer front panel keys is detected by pin 8 that is an ADC (analogue to digital converter). Pressing a switch will connect the 5V to the ground through a particular resistor that determines the value of the voltage on pin8 at that instant. This obtained value is comprehended by the micro and the corresponding operation is performed.

The ST92195 is the micro-controller, which is required for a color TV receiver. ST92195D1 is the version with one page Teletext and ST92195D7 is the one with 7 page Teletext. The IC has the supply voltage of 5 V and they are mounted in PSDIP package with 56 pins.

µ-Controller has the following features

- Display of the program number, channel number, TV Standard, analogue values, sleep timer, parental control and mute is done by OSD

- Single LED for stand-by and on mode indication

- System configuration with service mode

- 3 level logic output for SECAM and Tuner band switching

IC 501 controls all the functions of the receiver operated by the remote control and the front panel customer controls. It produces the on screen graphics, operates tuning, customers controls and engineering controls, and also incorporates all of the Teletext functions. It also controls the video processor, the audio processor, and the tuner. The circuits just mentioned are controlled via the I²C bus. Also IC501 controls the video source switching, vertical position adjustment and the vertical linearity adjustment via its ports.

An external 8K EEPROM is used by the micro. The EEPROM comes fully programmed. The main clock oscillator is 4.0 MHz crystal X501 on pins 50 and 51. Reset is provided on pin 2 via Q504. On switching on pin 2 becomes high and the controller gets reset which stays valid till a low signal comes on that pin.

Controls

Command information from the infrared remote controller is fed through the sensor IC502 to pin 1 of the microprocessor. Operation of the customer front panel keys is detected by pin 8 that is an ADC (analogue to digital converter). Pressing a switch will connect the 5V to the ground through a particular resistor that determines the value of the voltage on pin8 at that instant. This obtained value is comprehended by the micro and the corresponding operation is performed.

IC501 automatically switches from TV mode to AV1 by detecting the signal from or pin8 at the Scart connector, through it 56 pins.

Teletext

The microprocessor IC501 performs all of the Teletext functions internally. The Composite blanking video and Sync signal (CBVS) is input to pin 33 of the micro from pin 29 of IC403. When text is selected the text graphics are output as R.G.B signals on pins 15/16/17 of the micro and fed to pins 34/35/36 of IC403. At the same time pin 18 of the micro goes high taking pin 37 of IC403 high, blanking the picture and selecting text R.G.B. input.

Note: mixed mode is available and fast text with 8-page memory.

The microprocessor IC501 performs all of the Teletext functions internally. The Composite blanking video and Sync signal (CBVS) is input to pin 33 of the micro from pin 29 of IC403. When text is selected the text graphics are output as R.G.B signals on pins 15/16/17 of the micro and fed to pins 34/35/36 of IC403. At the same time pin 18 of the micro goes high taking pin 37 of IC403 high, blanking the picture and selecting text R.G.B. input.

Note: mixed mode is available and fast text with 8-page memory.

Video Path

The detected video signal is output from pins 18 of IC403, to sound traps Z403/404. The video is taken from the other side via the appropriate filter to Pin 18 of IC403. (1.2 p to p) Video to the Scart connectors is taken after R458 to Pin 19 of the Scart connector. The CVBS_TXT output Pin29 output is fed to IC501 Pin 34 (for Teletext). The video signal is sometimes labelled CVBS on the circuit diagram. This stands for Composite Video Blanking & Sync.

The composite signal is input Pin 13 (Video input) of IC403. This IC carries out all of the luma/Chroma processing internally and also provides the customer control functions of brightness, contrast, sharpness and saturation. IC403 is I²C bus controlled and incorporates auto grayscale circuitry and internal luma/chroma delay lines. The resulting R.G.B drive is output on pins 30,31 and 32. The R.G.B passes via connector PL405 to the CRT base PCB. Here the R.G.B signal is amplified by IC901 to provide drive for the cathodes of the CRT. IC901 produces a feedback signal, which is fed to IC403 (pin 33) for blanking and auto grayscale correction.

The detected video signal is output from pins 18 of IC403, to sound traps Z403/404. The video is taken from the other side via the appropriate filter to Pin 18 of IC403. (1.2 p to p) Video to the Scart connectors is taken after R458 to Pin 19 of the Scart connector. The CVBS_TXT output Pin29 output is fed to IC501 Pin 34 (for Teletext). The video signal is sometimes labelled CVBS on the circuit diagram. This stands for Composite Video Blanking & Sync.

The composite signal is input Pin 13 (Video input) of IC403. This IC carries out all of the luma/Chroma processing internally and also provides the customer control functions of brightness, contrast, sharpness and saturation. IC403 is I²C bus controlled and incorporates auto grayscale circuitry and internal luma/chroma delay lines. The resulting R.G.B drive is output on pins 30,31 and 32. The R.G.B passes via connector PL405 to the CRT base PCB. Here the R.G.B signal is amplified by IC901 to provide drive for the cathodes of the CRT. IC901 produces a feedback signal, which is fed to IC403 (pin 33) for blanking and auto grayscale correction.

Sound Path

The demodulated mono sound is taken from pin 55 of IC403 directly to the sound output stage IC401 Pin 7. The output signal from IC401 is Volume controlled achieved within IC403 using the I²C bus line from IC501. To limit the volume at the specified out put the A_out pin 55 is fed to IC 401 through a voltage divider R455 and R454. Muting of the output stage is provided from Pin 46 of IC501 to pin3 of IC401/6 of IC301.

IN the stereo model the IF from PINS 10 & 11 of the tuner passes through Z401 and the output signal goes through pins 1&2 of IC403. The output QSS signal from IC 403 is taken from pin 11 and sent to audio processor IC700. The left channel is output on PIN 29 and the right channel output is on PIN 28. Then to IC301 after passing through a voltage divider R454/R455 for the right channel and R463/R464 for the left channel.

IC403 handles also the AM modulated signals in L/L’ systems at pins 1&2.

The demodulated mono sound is taken from pin 55 of IC403 directly to the sound output stage IC401 Pin 7. The output signal from IC401 is Volume controlled achieved within IC403 using the I²C bus line from IC501. To limit the volume at the specified out put the A_out pin 55 is fed to IC 401 through a voltage divider R455 and R454. Muting of the output stage is provided from Pin 46 of IC501 to pin3 of IC401/6 of IC301.

IN the stereo model the IF from PINS 10 & 11 of the tuner passes through Z401 and the output signal goes through pins 1&2 of IC403. The output QSS signal from IC 403 is taken from pin 11 and sent to audio processor IC700. The left channel is output on PIN 29 and the right channel output is on PIN 28. Then to IC301 after passing through a voltage divider R454/R455 for the right channel and R463/R464 for the left channel.

IC403 handles also the AM modulated signals in L/L’ systems at pins 1&2.

DIGITAL TV sound processor MSP34X0

The MSP 34x0G is designed to perform demodulation of FM or AM-Mono TV sound.

Alternatively, two-carrier FM systems according to the German or Korean terrestrial specs or the satellite specs can be processed with the MSP 34x0G. Only the MSP 3410 does digital demodulation and decoding of NICAM-coded TV stereo sound. The MSP 34x0G offers a powerful feature to calculate the carrier field strength which can be used for automatic standard detection (terrestrial) and search algorithms (satellite).

The MSP 34x0G is designed to perform demodulation of FM or AM-Mono TV sound.

Alternatively, two-carrier FM systems according to the German or Korean terrestrial specs or the satellite specs can be processed with the MSP 34x0G. Only the MSP 3410 does digital demodulation and decoding of NICAM-coded TV stereo sound. The MSP 34x0G offers a powerful feature to calculate the carrier field strength which can be used for automatic standard detection (terrestrial) and search algorithms (satellite).

Sound output stage TDA7266L/TDA7266

TDA7266L is used as the AF output amplifier for mono applications. It is supplied by +12 VDC coming from a separate winding in the SMPS transformer. An output power of 4 W (THD = 0.5 %) can be delivered into an 16 ohm load.

TDA7266 is used as the AF output amplifier for stereo applications. It is supplied by +12 VDC coming from a separate winding in the SMPS transformer. An output power of 2*4W (THD = 0.5 %) can be delivered into an 16 ohm load.

TDA7266L is used as the AF output amplifier for mono applications. It is supplied by +12 VDC coming from a separate winding in the SMPS transformer. An output power of 4 W (THD = 0.5 %) can be delivered into an 16 ohm load.

TDA7266 is used as the AF output amplifier for stereo applications. It is supplied by +12 VDC coming from a separate winding in the SMPS transformer. An output power of 2*4W (THD = 0.5 %) can be delivered into an 16 ohm load.

Vertical output stage - TDA8174A

The TDA8174A is a power amplifier circuit for use in 90° and 110° color deflection systems for 25 to 200 Hz field frequencies, and for 4 : 3 and 16 : 9 picture tubes.

IC403 generates a vertical pulse signal VER_OUT and V_AMP that are fed to IC600 (the vertical stage IC). IC600 is supplied by a 26V DC via diode D610. It generates its own ramp signal and based on the V_AMP & VER_OUT signals it produces the vertical deflection signals that are fed to connector PL601. Vertical linearity adjustment is controlled by Q604, which is driven by the PWM output of IC501 at pin 49. Vertical position adjustment is conducted by Q606 derived by the VER_OUT signal. Switching Q606 will change the DC voltage on VOUT_2 pin, which will either lower or higher the picture. A DC level is supplied at VOUT_2 via D614 to stabilize the picture and make its position changeable.

The TDA8174A is a power amplifier circuit for use in 90° and 110° color deflection systems for 25 to 200 Hz field frequencies, and for 4 : 3 and 16 : 9 picture tubes.

IC403 generates a vertical pulse signal VER_OUT and V_AMP that are fed to IC600 (the vertical stage IC). IC600 is supplied by a 26V DC via diode D610. It generates its own ramp signal and based on the V_AMP & VER_OUT signals it produces the vertical deflection signals that are fed to connector PL601. Vertical linearity adjustment is controlled by Q604, which is driven by the PWM output of IC501 at pin 49. Vertical position adjustment is conducted by Q606 derived by the VER_OUT signal. Switching Q606 will change the DC voltage on VOUT_2 pin, which will either lower or higher the picture. A DC level is supplied at VOUT_2 via D614 to stabilize the picture and make its position changeable.

Power supply (SMPS)

The DC voltage required at various parts of the chassis are provided by an SMPS transformer controlled by the IC MC44608 which is designed for driving, controlling and protecting switching transistor of SMPS. The transformer produces 126 V (Flat models) or 116 V (non Flat models) for FBT input, +/- 14 V for audio output IC, S + 3.3, S + 5 V and 8 V for ST92195.

The ZX series of receivers incorporate a Motorola switch mode power supply using a MC 44608 regulator controller IC. The circuit provides power to the receiver in both standby and normal operation modes.

The DC voltage required at various parts of the chassis are provided by an SMPS transformer controlled by the IC MC44608 which is designed for driving, controlling and protecting switching transistor of SMPS. The transformer produces 126 V (Flat models) or 116 V (non Flat models) for FBT input, +/- 14 V for audio output IC, S + 3.3, S + 5 V and 8 V for ST92195.

The ZX series of receivers incorporate a Motorola switch mode power supply using a MC 44608 regulator controller IC. The circuit provides power to the receiver in both standby and normal operation modes.

Start Up

The switch on the mains supply is fed through the mains filter network TR801, the surge limiter resistor R828, the bridge rectifier diodes D811/13/37/38, and reservoir capacitor producing approx. 320 volts D.C. to feed the switching MOSFET Q801 via the primary winding of TR802 pins 6 and 7.

Start up resistor R801 feeds from a 500V coming from the mains through the adder diodes D809, D890 to pin 8 of IC800, the IC uses 9mA current source and connects it internally to VCC at pin6 allowing a rapid charge enough for start up. Then IC800 responds with the oscillator starting to oscillate at a 40 KHz frequency fixed by the IC manufacturer.

The IC then produces, pulse width modulation pulses, at this frequency on pin 5 to drive the base of the switching FET Q801, that will then switch current on and off through the primary of TR802, which will in turn provides voltages in the secondary windings. The secondary winding voltages being proportional to the length of time that Q801 is turned on in each cycle. The voltage produced between pins 4 and 3 of TR802 is rectified by D804 developing aprox. 12 volts on C810, which takes over from the start up resistor to supply pin 8 of IC800.

The Demag pin at pin1 offers 3 different functions: Zero voltage crossing detection (50mV), 24mA current detection and 120mA current detection. The 24mA level is used to detect the secondary reconfiguration status and the 120mA level to detect an Over Voltage status called Quick OVP.

The VCC at pin6 operates between 6,6V and 13V in normal operation, when this voltage exceeds 15V then the IC output is disabled.

The switch on the mains supply is fed through the mains filter network TR801, the surge limiter resistor R828, the bridge rectifier diodes D811/13/37/38, and reservoir capacitor producing approx. 320 volts D.C. to feed the switching MOSFET Q801 via the primary winding of TR802 pins 6 and 7.

Start up resistor R801 feeds from a 500V coming from the mains through the adder diodes D809, D890 to pin 8 of IC800, the IC uses 9mA current source and connects it internally to VCC at pin6 allowing a rapid charge enough for start up. Then IC800 responds with the oscillator starting to oscillate at a 40 KHz frequency fixed by the IC manufacturer.

The IC then produces, pulse width modulation pulses, at this frequency on pin 5 to drive the base of the switching FET Q801, that will then switch current on and off through the primary of TR802, which will in turn provides voltages in the secondary windings. The secondary winding voltages being proportional to the length of time that Q801 is turned on in each cycle. The voltage produced between pins 4 and 3 of TR802 is rectified by D804 developing aprox. 12 volts on C810, which takes over from the start up resistor to supply pin 8 of IC800.

The Demag pin at pin1 offers 3 different functions: Zero voltage crossing detection (50mV), 24mA current detection and 120mA current detection. The 24mA level is used to detect the secondary reconfiguration status and the 120mA level to detect an Over Voltage status called Quick OVP.

The VCC at pin6 operates between 6,6V and 13V in normal operation, when this voltage exceeds 15V then the IC output is disabled.

Voltage Regulation

After initial start up the secondary voltages of TR802 are established. These voltages then need to be regulated to the required levels. In a switch mode power supply such as this, it is the ON time of the switching FET Q801 that determines the output voltages produced. To provide regulation of the supply there is a feedback loop via an adjustable zener IC118 and an OPTO- coupler connected to pin3 of IC800. The reference voltage of IC118 is set to 2,5V to supply a B+ voltage of 115V. Any fluctuation at this pin will cause IC800 to compensate it either by increasing or decreasing the voltage at the secondary outputs.

After initial start up the secondary voltages of TR802 are established. These voltages then need to be regulated to the required levels. In a switch mode power supply such as this, it is the ON time of the switching FET Q801 that determines the output voltages produced. To provide regulation of the supply there is a feedback loop via an adjustable zener IC118 and an OPTO- coupler connected to pin3 of IC800. The reference voltage of IC118 is set to 2,5V to supply a B+ voltage of 115V. Any fluctuation at this pin will cause IC800 to compensate it either by increasing or decreasing the voltage at the secondary outputs.

Voltage Protection

The MC44608 offers two OVP functions:

1- A fixed function that detects when V CC is higher than 15.4V

2- A programmable function that uses the demag pin. The current flowing into the demag pin is mirrored and compared to the reference current Iovp (120mA). -Thus this OVP is quicker than normal number one as it directly senses the change in current rather than waiting for a specific voltage value, and is called QOVP. In both cases, once an OVP condition is detected, the output is latched off until a new circuit START–UP.

3- A software controlled function acts on pin52 of IC501. This pin monitors feedback from both 8V and 5V via D512, then compares these to a reference value Vref pre-set by the hardware through resistors R545, R546, R548. In normal mode operation 1.2V < Vref < 2.4V. Any voltage outside this window will cause the micro controller to force the TV to stand by mode by lowering the standby port. Refer to standby mode.

The MC44608 offers two OVP functions:

1- A fixed function that detects when V CC is higher than 15.4V

2- A programmable function that uses the demag pin. The current flowing into the demag pin is mirrored and compared to the reference current Iovp (120mA). -Thus this OVP is quicker than normal number one as it directly senses the change in current rather than waiting for a specific voltage value, and is called QOVP. In both cases, once an OVP condition is detected, the output is latched off until a new circuit START–UP.

3- A software controlled function acts on pin52 of IC501. This pin monitors feedback from both 8V and 5V via D512, then compares these to a reference value Vref pre-set by the hardware through resistors R545, R546, R548. In normal mode operation 1.2V < Vref < 2.4V. Any voltage outside this window will cause the micro controller to force the TV to stand by mode by lowering the standby port. Refer to standby mode.

Current Protection

To monitor the current drawn by the receiver the source of Q801 is returned to the bridge rectifier through a low value resistor R807. All the current drawn by the receiver will flow through that resistor each time Q801 conducts; this will produce a voltage across the resistors proportional to the current drawn by the receiver. This voltage is fed to pin 2 of IC800 via R806. When the receiver is working normally the voltage across R807 is only a fraction of a volt and is not large enough to have any effect on IC800. Under fault conditions, if the receiver draws excessive current the voltage across R807 will rise. This voltage is monitored by the current sense input pin2.

To monitor the current drawn by the receiver the source of Q801 is returned to the bridge rectifier through a low value resistor R807. All the current drawn by the receiver will flow through that resistor each time Q801 conducts; this will produce a voltage across the resistors proportional to the current drawn by the receiver. This voltage is fed to pin 2 of IC800 via R806. When the receiver is working normally the voltage across R807 is only a fraction of a volt and is not large enough to have any effect on IC800. Under fault conditions, if the receiver draws excessive current the voltage across R807 will rise. This voltage is monitored by the current sense input pin2.

This Current Sense pin senses the voltage developed on the series resistor R806 inserted in the source of the power MOSFET. When I sense reaches 1V, the Driver output (pin 5) is disabled. This is known as the Over Current Protection function. A 200mA current source is flowing out of the pin 3 during the start–up phase and during the switching phase in case of the Pulsed Mode of operation. A resistor can be inserted between the sense resistor and the pin 3, thus a programmable peak current detection can be performed during the SMPS stand–by mode.

Standby Operation

As mentioned earlier the Start–up Management of MC44608 is as follows:

The Vi pin 8 of IC800 is directly connected to the HV DC rail Vin. This high voltage current source is internally connected to the VCC pin and thus issued to charge the VCC capacitor. The V CC capacitor charge period corresponds to the Start–up phase. When the V CC voltage reaches 13V, the high voltage 9mA current source is disabled and the device starts working. The device enters into the switching phase.

To help increase the application safety against high voltage spike on pin8 a small wattage 1k _ series resistor is inserted between the Vin rail and pin 8. After this start-up the IC can distinguish between the different modes of operation using the following technique:

As mentioned earlier the Start–up Management of MC44608 is as follows:

The Vi pin 8 of IC800 is directly connected to the HV DC rail Vin. This high voltage current source is internally connected to the VCC pin and thus issued to charge the VCC capacitor. The V CC capacitor charge period corresponds to the Start–up phase. When the V CC voltage reaches 13V, the high voltage 9mA current source is disabled and the device starts working. The device enters into the switching phase.

To help increase the application safety against high voltage spike on pin8 a small wattage 1k _ series resistor is inserted between the Vin rail and pin 8. After this start-up the IC can distinguish between the different modes of operation using the following technique:

Mode Transition

The LW latch is the memory of the working status at the end of every switching sequence. Two different cases must be considered for the logic at the termination of the SWITCHING PHASE:

1. No Over Current was observed

2. An Over Current was observed

These two cases correspond to the two signals “NOC” in case of “No Over Current” and “OC” in case of Over Current.

The effective working status at the end of the ON time memorised in LW corresponds to Q=1 for no over current, and Q=0 for over current.

To enter the standby mode secondary side is reconfigured using D889 loop, this starts with the microprocessor ‘s pin 47 becomes high; as the standby port becomes high Q503 conducts and Q802 becomes off then D889 conducts and the high voltage output value becomes lower than the NORMAL mode regulated value. The shunt regulator IC118 is fully OFF. In the SMPS stand–by mode all the SMPS outputs are lowered except for the low voltage output that supply the wake–up circuit located at the isolated side of the power supply. In that mode the secondary regulation is performed by the Zener diode (D801) connected in parallel to the TL431. The secondary reconfiguration status can be detected on the SMPS primary side by measuring the voltage level at pin4 of TR802.

In the SMPS stand–by mode the 3 distinct phases are:

The SWITCHING PHASE: Similar to the Overload mode. The current sense clamping level is reduced. When VCC crosses the current sense section, the C.S. clamping level depends on the power to be delivered to the load during the SMPS stand–by mode. Every switching sequence ON/OFF is terminated by an OC as long as the secondary Zener

diode voltage has not been reached. When the Zener voltage is reached the ON cycle is terminated by a true PWM action. The proper SWITCHING PHASE termination must correspond to a NOC condition. The LW latch stores this NOC status. The LATCHED OFF PHASE: The MODE latch is set.

The START–UP PHASE is similar to the Overload Mode. The MODE latch remains in its set status (Q=1).

The SWITCHING PHASE: The Stand-by signal is validated and the 200uA is sourced out of the Current Sense pin 2.

The LW latch is the memory of the working status at the end of every switching sequence. Two different cases must be considered for the logic at the termination of the SWITCHING PHASE:

1. No Over Current was observed

2. An Over Current was observed

These two cases correspond to the two signals “NOC” in case of “No Over Current” and “OC” in case of Over Current.

The effective working status at the end of the ON time memorised in LW corresponds to Q=1 for no over current, and Q=0 for over current.

To enter the standby mode secondary side is reconfigured using D889 loop, this starts with the microprocessor ‘s pin 47 becomes high; as the standby port becomes high Q503 conducts and Q802 becomes off then D889 conducts and the high voltage output value becomes lower than the NORMAL mode regulated value. The shunt regulator IC118 is fully OFF. In the SMPS stand–by mode all the SMPS outputs are lowered except for the low voltage output that supply the wake–up circuit located at the isolated side of the power supply. In that mode the secondary regulation is performed by the Zener diode (D801) connected in parallel to the TL431. The secondary reconfiguration status can be detected on the SMPS primary side by measuring the voltage level at pin4 of TR802.

In the SMPS stand–by mode the 3 distinct phases are:

The SWITCHING PHASE: Similar to the Overload mode. The current sense clamping level is reduced. When VCC crosses the current sense section, the C.S. clamping level depends on the power to be delivered to the load during the SMPS stand–by mode. Every switching sequence ON/OFF is terminated by an OC as long as the secondary Zener

diode voltage has not been reached. When the Zener voltage is reached the ON cycle is terminated by a true PWM action. The proper SWITCHING PHASE termination must correspond to a NOC condition. The LW latch stores this NOC status. The LATCHED OFF PHASE: The MODE latch is set.

The START–UP PHASE is similar to the Overload Mode. The MODE latch remains in its set status (Q=1).

The SWITCHING PHASE: The Stand-by signal is validated and the 200uA is sourced out of the Current Sense pin 2.

SMPS Switch Off

When the mains is switched OFF, so long as the electrolytic bulk capacitor provides energy to the SMPS the controller remains in the switching phase. Then the peak current reaches its maximum peak value, the switching frequency decreases and all the secondary voltages are reduced. The V CC voltage is also reduced. When VCC is less than 6,5V, the SMPS stops working

When the mains is switched OFF, so long as the electrolytic bulk capacitor provides energy to the SMPS the controller remains in the switching phase. Then the peak current reaches its maximum peak value, the switching frequency decreases and all the secondary voltages are reduced. The V CC voltage is also reduced. When VCC is less than 6,5V, the SMPS stops working

Line circuit

Line and frame drive are generated by IC403. The sync pulses are separated from the incoming video signal at pin 18/ 20/22 and used to control the internal circuitry of the IC. Line drive is produced by counting down the external 4.43 MHz crystal at pin 40 to 15.625 KHz locked to the incoming sync. This drive is output on pin 48 and feeds directly to the line drive transistor Q601. Note. That the output of IC403 Pin 48 is an open-collector and requires a pull up resistor, if the pin is open circuited for test no waveform will be seen. Q601 collector feeds the line output transistor Q603.

The line output stage is conventional with a transformer containing a split diode winding for EHT generation. Fifth harmonic tuning is achieved by capacitor C618/619.

A fly-back pulse is taken from pin 1 of the FBT transformer. This is required by IC403 (Pin 49) for burst / sync gating, and RGB line blanking. The ver_sync signal is output from the pin47 and fed to Pin41 of IC501. The H_sync pulse is taken from pin 1 of the FBT and fed to the micro at pin 40. These two signals are required by the micro for graphics timing and also for text.

Line and frame drive are generated by IC403. The sync pulses are separated from the incoming video signal at pin 18/ 20/22 and used to control the internal circuitry of the IC. Line drive is produced by counting down the external 4.43 MHz crystal at pin 40 to 15.625 KHz locked to the incoming sync. This drive is output on pin 48 and feeds directly to the line drive transistor Q601. Note. That the output of IC403 Pin 48 is an open-collector and requires a pull up resistor, if the pin is open circuited for test no waveform will be seen. Q601 collector feeds the line output transistor Q603.

The line output stage is conventional with a transformer containing a split diode winding for EHT generation. Fifth harmonic tuning is achieved by capacitor C618/619.

A fly-back pulse is taken from pin 1 of the FBT transformer. This is required by IC403 (Pin 49) for burst / sync gating, and RGB line blanking. The ver_sync signal is output from the pin47 and fed to Pin41 of IC501. The H_sync pulse is taken from pin 1 of the FBT and fed to the micro at pin 40. These two signals are required by the micro for graphics timing and also for text.

B.C.L Circuit (Beam Current Limiter)

Beam current limiting is employed to protect the circuitry in the receiver, the CRT and to prevent excessive X Ray radiation in fault conditions. The current drawn by the CRT is monitored by the current drawn through the winding of the fly-back transformer that produces the EHT for the CRT anode. The end of the winding (Pin 10) is returned to IC403

Pins 46, the beam current drawn by the CRT passes through Q603 and develops a voltage on the collector proportional to the current (V=IxR).

The voltage on the collector will vary depending on the beam current being drawn reducing the brightness and contrast of the picture. If the voltage is sufficiently negative (indicating very high excess beam current) the output will be reduced, reducing the picture brightness and contrast.

Beam current limiting is employed to protect the circuitry in the receiver, the CRT and to prevent excessive X Ray radiation in fault conditions. The current drawn by the CRT is monitored by the current drawn through the winding of the fly-back transformer that produces the EHT for the CRT anode. The end of the winding (Pin 10) is returned to IC403

Pins 46, the beam current drawn by the CRT passes through Q603 and develops a voltage on the collector proportional to the current (V=IxR).

The voltage on the collector will vary depending on the beam current being drawn reducing the brightness and contrast of the picture. If the voltage is sufficiently negative (indicating very high excess beam current) the output will be reduced, reducing the picture brightness and contrast.

Serial access CMOS 8K EEPROM 24C08

The 24C08 is a 8 Kbit electrically erasable programmable memory (EEPROM), organized as 4 blocks of 256*08 bits.

The memory is compatible with the I²C standard, two wire serial interface which uses a bi-directional data bus and serial clock.

The 24C08 is a 8 Kbit electrically erasable programmable memory (EEPROM), organized as 4 blocks of 256*08 bits.

The memory is compatible with the I²C standard, two wire serial interface which uses a bi-directional data bus and serial clock.

EEPROM Initialization

If the E²PROM IC500 is replaced it will come fully programmed and therefore it is not necessary to initialize the new device. In some circumstances the E²PROM may become corrupted in use i.e. static discharge or lightning strike. If this happens, it is advised that the E²PROM is replaced.

If the E²PROM IC500 is replaced it will come fully programmed and therefore it is not necessary to initialize the new device. In some circumstances the E²PROM may become corrupted in use i.e. static discharge or lightning strike. If this happens, it is advised that the E²PROM is replaced.

MSP34X0G

The MSP 34x0G family of single-chip Multistandard Sound Processors covers the sound processing of all analog TVStandards worldwide, as well as the NICAM digital sound standards. The full TV sound processing, starting with analog sound IF signal-in, down to processed analog AF-out, is performed on a single chip. Figure 3 shows a simplified functional block diagram of the MSP 34x0G. This new generation of TV sound processing ICs now includes versions for processing the multichannel television sound (MTS) signal conforming to the standard recommended by the Broadcast

Television Systems Committee (BTSC). The DBX noise reduction, or alternatively, Micronas Noise Reduction (MNR) is performed alignment free.

Other processed standards are the Japanese FM-FM multiplex standard (EIA-J) and the FM Stereo Radio standard.

Current ICs have to perform adjustment procedures in order to achieve good stereo separation for BTSC and EIA-J.

The MSP 34x0G has optimum stereo performance without any adjustments. All MSP 34xxG versions are pin compatible to the MSP 34xxD. Only minor modifications are necessary to adapt a MSP 34xxD controlling software to the MSP 34xxG. The MSP 34x0G further simplifies controlling software.

Standard selection requires a single I2C transmission only. The MSP 34x0G has built-in automatic functions: The IC is able to detect the actual sound standard automatically (Automatic Standard Detection).

The MSP 34x0G family of single-chip Multistandard Sound Processors covers the sound processing of all analog TVStandards worldwide, as well as the NICAM digital sound standards. The full TV sound processing, starting with analog sound IF signal-in, down to processed analog AF-out, is performed on a single chip. Figure 3 shows a simplified functional block diagram of the MSP 34x0G. This new generation of TV sound processing ICs now includes versions for processing the multichannel television sound (MTS) signal conforming to the standard recommended by the Broadcast

Television Systems Committee (BTSC). The DBX noise reduction, or alternatively, Micronas Noise Reduction (MNR) is performed alignment free.

Other processed standards are the Japanese FM-FM multiplex standard (EIA-J) and the FM Stereo Radio standard.

Current ICs have to perform adjustment procedures in order to achieve good stereo separation for BTSC and EIA-J.

The MSP 34x0G has optimum stereo performance without any adjustments. All MSP 34xxG versions are pin compatible to the MSP 34xxD. Only minor modifications are necessary to adapt a MSP 34xxD controlling software to the MSP 34xxG. The MSP 34x0G further simplifies controlling software.

Standard selection requires a single I2C transmission only. The MSP 34x0G has built-in automatic functions: The IC is able to detect the actual sound standard automatically (Automatic Standard Detection).

Furthermore, pilot levels and identification signals can be evaluated internally with subsequent switching between mono/ stereo/bilingual; no I2C interaction is necessary (Automatic Sound Selection). The MSP 34x0G can handle very high FM deviations even in conjunction with NICAM processing. This is especially important for the introduction of NICAM in China. The ICs are produced in submicron CMOS technology.

Service Menu(Service mode)

All system, geometry and white balance alignments are performed in Service Mode. Before starting the service mode alignments, make sure that all manual adjustments are done correctly.

To enter the service mode:

1. Press the MENU (30) button on the remote control gun.

All system, geometry and white balance alignments are performed in Service Mode. Before starting the service mode alignments, make sure that all manual adjustments are done correctly.

To enter the service mode:

1. Press the MENU (30) button on the remote control gun.

2. Press digit keys 4, 7, 2 and 5 consecutively.

1. Use the CURSOR UP (2) / DOWN (31) buttons to move between the registers.

2. Use the CURSOR LEFT (32) / RIGHT (3) buttons to change the data. See figure 5.

To memorize the adjustment:

It is not required to memorize the adjustment. Data are stored automatically.

To exit the Service Mode:

Switch the TV off using the mains switch.

To memorize the adjustment:

It is not required to memorize the adjustment. Data are stored automatically.

To exit the Service Mode:

Switch the TV off using the mains switch.

Service Adjustments default values.

Using Colored Buttons

By using the four coloured buttons on the remote control different features or adjust may be accessed.

By using the four coloured buttons on the remote control different features or adjust may be accessed.

AVL

Press the RED button to activate or deactivate the AVL (Automatic Volume Level, between different broadcast channels).

Press the RED button to activate or deactivate the AVL (Automatic Volume Level, between different broadcast channels).

GEOMETRY MENU

Press the GREEN button in order to change from the Main Service Menu to the Geometry Menu,

Press the GREEN button in order to change from the Main Service Menu to the Geometry Menu,

To return to the Main Service Menu it should be pressed the Menu button.

In the bottom area of this Menu, it can be seen “AUTO”. By pressing the WIDE MODE button it changes to 4:3 or 16:9 format. To perform the Geometry adjustments select the most suitable option:

- AUTO, entering 4:3 or 16:9 signal and proceeding with adjustments as below.

- 4:3, entering 4:3 signal and proceeding with adjustments as below.

- 16:9, entering 16:9 signal and proceeding with adjustments.

- AUTO, entering 4:3 or 16:9 signal and proceeding with adjustments as below.

- 4:3, entering 4:3 signal and proceeding with adjustments as below.

- 16:9, entering 16:9 signal and proceeding with adjustments.